(1)系统抗干扰电路板设计 抗干扰问题是现代电路板设计中一个很重要的环节,它直接反映了整个系统的性能和工作的可靠性。在飞轮储能系统的电力电子控制中,由于其高压和低压控制信号同时并存,而且功率晶体管的瞬时开关也产生很大的电磁干扰,因此提高系统的抗干扰能力也是该系统设计的一个重要环节。形成干扰的主要原因有如下几点:

1)干扰源,是指产生干扰的元件、设各或信号,用数字语言描述是指du/dt、di/dt大的地方。干扰按其来源可分为外部干扰和内部干扰:外部干扰是指那些与仪表的结构无关,由使用条件和外界环境因素决定的干扰,如雷电、交流供电、电机等;内部干扰是由仪表结构布局及生产工艺决定的,如多点接地选成的电位差引起的干扰、寄生振荡引起的干扰、尖峰或振铃噪声引起的干扰等。

2)敏感器件,指容易被干扰的对象,如微控制器、存贮器、A/D转换、弱信号处理电路等。

3)传播路径,是干扰从干扰源到敏感器件传播的媒介,典型的干扰传播路径是通过导线的传导、电磁感应、静电感应和空间的辐射。

抗干扰电路板设计的基本任务是系统或装置既不因外界电磁干扰影响而误动作或丧失功能,也不向外界发送过大的噪声干扰,以免影响其他系统或装置正常工作。其设计一般遵循下列三个原则:抑制噪声源,直接消除干扰产生的原因;切断电磁干扰的传播途径,或者提高传递途径对电磁干扰的衰减作用,以消除噪声源和受扰设各之间的噪声耦合;加强受扰设各抵抗电磁干扰的能力,降低噪声敏感度。目前,对系统的采用的抗干扰技术主要有硬件抗干扰技术和软件抗干扰技术。

1)硬件抗干扰技术的电路板设计。飞轮储能系统的逆变电路高达20kHz的载波信号决定了它会产生噪声,这样系统中电力电子装置所产生的噪声和谐波问题就成为主要的干扰,它们会对设备和附近的仪表产生影响,影响的程度与其控制系统和设各的抗干扰能力、接线环境、安装距离及接地方法等因素有关。

转换器产生的PWM信号是以高速通断DC电压来控制输出电压波形的。急剧的上升或下降的输出电压波包含许多高频分量,这些高频分量就是产生噪声的根源。虽然噪声和谐波都对电子设各运行产生不良影响,但是两者还是有区别的:谐波通常是指50次以下的高频分量,频率为2~3kHz;而噪声却为10kHz甚至更高的高频分量。噪声一般要分为两大类:一类是由外部侵入到飞轮电池的电力电子装置,使其误动作:另一类是该装置本身由于高频载波产生的噪声,它对周围电子、电信设各产生不良影响。

减低噪声影响的一般办法有改善动力线和信号线的布线方式,控制信号用的信号线必须选用屏蔽线,屏蔽线外皮接地。为防止外部噪声侵入,可以采取以下的措施:使该电力电子装置远离噪声源、信号线采取数字滤波和屏蔽线接地。

电路板设计噪声的衰减技术有如下几点:

①电线噪声的衰减的方法:在交流输入端接入无线电噪声滤波器;在电源输入端和逆变器输出端接入线噪声滤波器,该滤波器可由铁心线圈构成;将无线电噪声滤波器和线噪声滤波器联合使用;在电源侧接人LC滤波器。

②逆变器至电机配线噪声辐射衰减,可采取金属导线管和金属箱通过接地来切断噪声辐射。

③飞轮电力电子装置的辐射噪声的衰减,通常其噪声辐射是很小的,但是如果周围的仪器对噪声很敏感,则应把该装置装入金属箱内屏蔽起来。

对于模拟电路干扰的抑制,由于电路中有要测量的电流、电压等模拟量,其输出信号都是微弱的模拟量信号,极易受干扰影响,在传输线附近有强磁场时,信号线将有较大的交流噪声。可以通过在放大器的输入、输出之间并联一个电容,在输入端接入有源低通滤波器来有效地抑制交流噪声。此外,在A/D变换时,数字地线和模拟电路地线分开,在输入端加入箝位二极管,防止异常过压信号。

而数字电路常见的干扰有电源噪声、地线噪声、串扰、反射和静电放电噪声。为抑制噪声,应注意输入与输出线路的隔离,线路的选择、配线、器件的布局等问题。输入信号的处理是抗干扰的重要环节,大量的干扰都是从此侵入的,一般可以从以下几个方面采取措施:

①接点抖动干扰的抑制;多余的连接线路要尽量短,尽量用相互绞合的屏蔽线作输入线,以减少连线产生的杂散电容和电感;避免信号线与动力线、数据线与脉冲线接近。

②采用光电隔离技术,并且在隔离器件上加RC电路滤波。

③认真妥善处理好接地问题,如模拟电路地与数字电路地要分开,印制板上模拟电路与数字电路应分开,大电流地应单独引至接地点,印制板地线形成网格要足够宽等。

2)软件抗干扰技术。除了硬件上要采取一系列的抗干扰措施外,在软件上也要采取数字滤波、设置软件陷阱、利用看门狗程序冗余设计等措施使系统稳定可靠地运行。特别地,当储能飞轮处于某一工作状态的时间较长时,在主循环中应不断地检测状态,重复执行相应的操作,也是增强可靠性的一个方法。

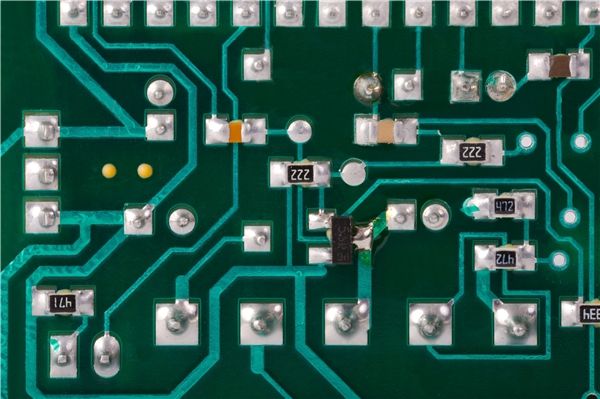

(2)电路板设计 由于DSP控制器工作频率较高,即使电路原理图设计正确,若印制电路板设计不当,也会对DSP控制器的可靠性产生不利影响。例如,如果印制板两条细平行线靠得很近,则会形成信号波形的延迟,在传输线的终端形成反射噪声。因此,在设计DSP控制器印制电路板时,应注意采用正确的方法。

1)地线设计。在DSP电路中,接地是控制干扰的重要方法,如能将接地和屏蔽正确结合起来使用,可解决大部分干扰问题。在一块电路板上,DSP控制器同时集成了数字电路和模拟电路,设计电路板时,应使它们尽量分开,而两者的地线不要相混,分别与电源端地线相连。尽量加粗接地线,同时将接地线构成闭环路。

2)配置去耦电容。在直流电源回路中,负载的变化会引起电源噪声。例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。配置去耦电容可以抑制因负载变化而产生的噪声,是DSP电路板的可靠性设计的一种常规做法:电源输人端可跨接一个10~100μF的电解电容器;为每个集成电路芯片配置一个0.01 μF的陶瓷电容器;对于关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线和地线间直接接入去耦电容。注意去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

3)电路板器件的布置。在器件布置方面与其他逻辑电路一样,应把相互有关的器件尽量放得靠近些,这样可以获得较好的抗噪声效果。时钟发生器、晶振和CPU的时钟输人端都易产生噪声,这些器件要相互靠近些,同时远离模拟器件。

提高开关频率可以减小电感值,从而减小电感的体积,但受功率管开关频率和开关损耗限制,合理的开关频率为10~20kHz,这里定为20kHz。