time : 2019-10-14 09:11 作者:凡亿pcb

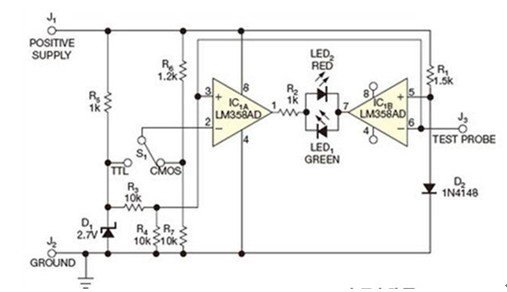

IC1A的非反相输入端与IC1B的反相输入端连接到测试探头上。电路使用90%的电源电压作为CMOS逻辑高,2.7V作为TTL逻辑高。

TTL和 CMOS都用0.7V作为逻辑低,因为它们逻辑低的电平都接近0.7V。分压器R3/R4对2.7V的齐纳二极管D1电压作分压,为IC1A的非反相输入 端和IC1B的反相输入端提供1.35V。二极管D2为正偏,D2上的0.7V电压就是低限,代表逻辑低。在IC1B的非反相输入端设定此电压。

在TTL模式下,IC1A 反相输入端的电压为2V。在CMOS模式下,IC1A反相输入端的电压接近于通过分压器R6/R7输入电压的90%。无论是CMOS或TTL模式,当探头为高阻态时,IC1A的反相输入端电压大于其1.3V的非反相输入端电压。

IC1A的输出为低。IC1B的1.3V反相输入端电压大于其0.7V的非反相 输入端电压。IC1B的输出也为低,两只LED均熄灭。在TTL模式下,当测量逻辑高时,IC1A的2.7V反相输入电压小于其非反相输入电压,即探头电压。IC1A的输出为高。IC1B的反相输入电压(即探头电压)大于其0.7V的非反相输入电压。因此,IC1B的输出为低。红色LED发光,表示为逻辑高。

逻辑探头电路图