pcb打样厂家(凡亿PCB)作为专业的

pcb打样制造商,专注于PCB打样和PCB线路板的生产制造。今天就让

凡亿PCB,SMT贴片加工,凡亿PCB在线下单,电路板打样,线路板打样,PCB板,电路板厂,PCB设计,线路板厂带大家一起了解一下pcb打样之基于DSP的高速

PCB抗干扰设计.

pcb打样1 DSP系统的干扰产生分析为了做出一个稳定可靠的DSP系统,必须从各个方面来消除干扰,即使不能完全消除,也要尽量减少到最小。对于DSP系统而言,主要干扰来自于以下几个方面:①输入输出通道干扰。指干扰通过前向通道和后向通道进入系统,如DSP系统的数据采集环节,干扰通过传感器迭加到信号上,使数据采集的误差增大。在输出环节,干扰可以将输出的数据误差增大,甚至完全错误,造成系统崩溃。可以合理利用光耦器件减小输入输出通道干扰,对于传感器和DSP主系统的干扰可利用电气隔离来阳档千扰讲入。②电源系统的干扰。整个DSP系统的主要干扰源。电源在向系统提供电能的同时也将其噪声加到供电的电源上,必须在电源芯片电路设计时对电源线进行退耦。③空间辐射耦合干扰。经过辐射的耦合通常称为串扰。串扰发生在电流流经导线时产生的电磁场,而电磁场在邻近的导线中感应瞬态电流,造成临近的信号失真,甚至错误。串扰的强度取决于器件、导线的几何尺寸及相隔距离。在DSP布线时,信号线间距越大,距离地线越近,就越可以有效地减小串扰。 2 针对产生干扰的原因设计PCB下面给出如何在DSP系统的PCB制作过程中减小各种干扰的方法。

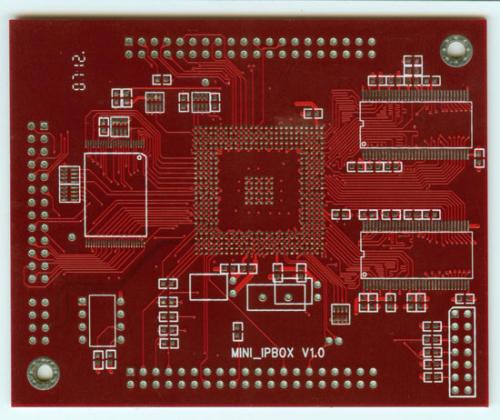

pcb打样 多层板的层叠式设计DSP高速数字电路中,为了提高信号质量,降低布线难度,增加系统的EMC,一般采用多层板的层叠式设计。层叠式设计可以提供最短的回流路径,减小耦合面积,抑制差模干扰。在层叠式设计中,分配专门的电源层和地层,并且地层和电源层紧耦合对抑制共模干扰有好处(利用相邻的平面降低电源平面交流阻抗)。以图1所示的4层板为例来说明层叠式的设计方案。采用这种4层PCB设计的结构有很多优点。在顶层(top层)下面有一层电源层,元器件的电源引脚可以直接接到电源,不用穿过地平面。关键的信号选布在底层(bottorn层),使重要的信号走线空间更大,器件尽量放在同一层面上。若没有必要,不要做2层零件的板子,这样会增加装配时间和装配复杂度。如top层,只有当top层组件过密时,才将高度有限并且发热量小的器件,像退耦电容(贴片)放在bottom层。对于DSP系统可能有大量的线要布,采用层叠式设计,可以在内层走线。如果按照传统的通孔会浪费很多宝贵的走线空间,可以利用盲埋孔(blind/buried via)来增加走线面积。

pcb打样布局设计为了使DSP系统获得最佳性能,元器件的布局是非常重要的。首先放置DSP、Flash、SRAM和CPLD器件,这耍慎重考虑走线空间,然后按功能独立原则放置其他IC,最后考虑I/O口的放置。结合以上布局再考虑PCB的尺寸:若尺寸过大,会使印制线条太长,阻抗增加,抗噪声能力下降,制板费用也会增加;如果PCB太小,则散热不好,而且空间有限,邻近的线条容易受到干扰。所以要根据实际需要选择器件,结合走线空间,大体上算出PCB的大小。在对DSP系统布局时,以下器件的摆放位置要特别注意。

(1) 高速信号布局在整个DSP系统中,DSP与Flash、SRAM之间是主要的高速数字信号线,所以器件之间的距离要尽量近,其连线尽可能短,并且直接连接。因此,为了减小传输线对信号质量的影响,高速信号走线应尽量短。还要考虑到很多速度达到几百MHz的DSP芯片,需要做蛇型绕线(delay tune)。这在下面布线中将重点阐述。

(2) 数模器件布局在DSP系统中大多不是单一的功能电路,大量应用了CM0S的数字器件和数字模拟混合器件,所以要将数/模分开布局。模拟信号器件尽量集中,使模拟地能够在整个数字地中间画出一个独立的属于模拟信号的区域,避免数字信号对模拟信号的干扰。对于一些数模混合器件,如D/A转换器,传统上将其看作模拟器件,把它放在模拟地上,并且给其提供一个数字回路,让数字噪声反馈回信号源,减小数字噪声对模拟地的影响。

(3) 时钟的布局对于时钟、片选和总线信号,应尽量远离I/O线和接插件。DSP系统的时钟输入,很容易受到干扰,对它的处理非常关键。要始终保证时钟产生器尽量靠近DSP芯片,使时钟线尽量短。时钟晶体振荡器的外壳最好接地。

(4)退耦布局为了减小集成电路芯片电源上的电压瞬时过冲,对集成电路芯片加退耦电容,这样可以有效地去除电源上毛刺的影响,并减少在PCB上的电源环路反射。加退耦电容可以旁路掉集成电路器件的高频噪声,还可以作为储能电容,提供和吸收集成电路开关门瞬间的充放电能。

pcb打样在DSP系统中,对各个集成电路安放退耦电容,像DSP、SRAM、Flash等,在芯片的每个电源和地之间添加,而且要特别注意,退耦电容要尽量靠近电源提供端(source)和IC的零件脚(pin)。保证从电源提供端(sotlrce端)和进入IC的电流的纯净,并且尽量能让噪音的路径缩短。如图2所示,处理电容时,使用大的过孔或多个过孔,且过孔到电容间的连线应尽量短、粗。2个过孔距离远时,因为路径太大,不好;最好的就是退耦电容的2个过孔越近越好,可以使噪声以最短路径到地。

pcb打样厂家(凡亿PCB)专注pcb打样研发制造10年。交期短,服务好,品质优。怎么样?你是否对pcb打样之基于DSP的高速PCB抗干扰设计有了一定的了解了呢!点滴学习汇聚成海哦!