射频(RF)电路板设计尽管在理论上还有许多不确定性,但RF电路板设计還是有很多能够遵照的规律。但是,在具体设计时,真实好用的方法是当这种规律因各种限定而没法执行时,怎样对他们开展折中解决,文中将集中讨论与射频电路板分区设计相关的各种难题。

01 微过孔的种类

电路板上不一样特性的电路务必隔开,可是又要不在造成干扰信号的最好状况下联接,这就必须采用微过孔(microvia)。一般微过孔直徑为0.05mm~0.22mm,这种过孔一般分成三类,即埋孔(blindvia)、埋孔(buryvia)和埋孔(throughvia)。埋孔坐落于印刷电路板的高层和最底层表层,具备一定深层,用以表面路线和下边的里层路线的联接,孔的深层一般不超过一定的比例(直径)。埋孔就是指坐落于印刷电路板里层的联接孔,它不容易拓宽到pcb线路板的表层。所述两大类孔都坐落于pcb线路板的里层,压层前运用埋孔成形工艺进行,在过孔产生全过程中将会还会继续重合搞好好多个里层。第三种称之为埋孔,这类孔越过全部pcb线路板,可用以完成內部互联或做为部件的粘着精准定位孔。

02 选用分区方法

在设计RF电路板时,应尽量把大功率RF放大仪(HPA)和低噪声放大仪(LNA)防护起来,简易的说,便是让大功率RF发送电路杜绝低噪声接受电路。假如PCB板上带许多室内空间,那麼能够非常容易地保证这一点。但一般零组件许多时,PCB生产制造室内空间便会变的不大,因而它是没办法做到的。能够把他们放到PCB板的双面,或是让他们更替工作中,而不是另外工作中。大功率电路有时候还可包含RF油压缓冲器(buffer)和压控振荡器(VCO)。

设计分区能够分为实体分区(physicalpartitioning)和电气设备分区(Electricalpartitioning)。实体分区关键涉及到零组件合理布局、方向和屏蔽掉等难题;电气设备分区能够再次分为电源分派、RF布线、比较敏感电路和数据信号、接地装置等分区。

03 实体分区

零组件合理布局是完成一个出色RF设计的重要,最有效的技术性是最先固定不动坐落于RF相对路径上的零组件,并调节其方向,使RF相对路径的长短减到最少。并使RF键入杜绝RF輸出,并尽量杜绝大功率电路和低噪声电路。

最有效的电路板堆栈方式是将主接地装置分配在表层下的第二层,并尽量将RF线走在表面上。将RF相对路径上的过孔规格减到最少不但能够降低相对路径电感,并且还能够降低主接地面上的空焊点,并可降低RF动能泄露到堆叠板内其他地区的机遇。

在实体室内空间上,像多级别放大仪那样的线形电路一般得以将好几个RF区中间互相防护起来,可是双工器、混频器和高频放大仪一直有好几个RF/IF数据信号互相影响,因而务必小心地将这一危害减到最少。RF与IF布线应尽量走十字交叉,并尽量在他们中间隔一块接地装置总面积。恰当的RF相对路径对一整块PCB板的特性来讲十分关键,这也就是为何零组件合理布局一般在移动手机PCB板设计中占绝大部分時间的缘故。

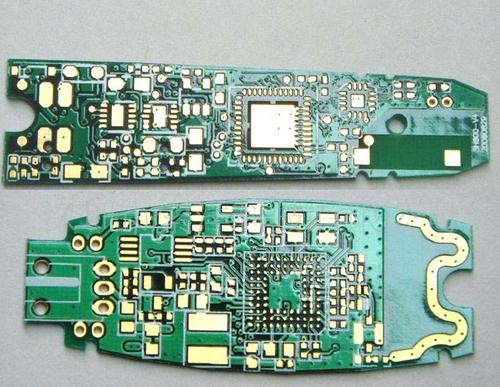

在移动手机PCB板上,一般能够将低噪声放大仪电路放到PCB打样版的某一面,而高功率放大器放到另一面,并最后意谓双工器在同一表面将他们联接到RF无线天线的一端和基频CPU的另一端。这必须一些方法来保证RF动能不容易意谓过孔,从板的一面传送到另一面,常见的技术性是在双面都应用埋孔。能够意谓将埋孔分配在PCB板双面也不受RF影响的地区,来将过孔的不好危害减到最少。

04 金属屏蔽罩

有时候,不大可能在好几个电路区块链中间保存充足的区别,在这类状况下就务必考虑到选用金属屏蔽罩将频射动能屏蔽掉在RF地区内,但金属屏蔽罩也是有不良反应,比如:制造成本和安装成本费都很高。

外观设计不规律的金属屏蔽罩在生产制造时没办法确保高精度,正方形或方形金属屏蔽罩又使零组件合理布局遭受一些限定;金属屏蔽罩不利零组件拆换和常见故障挪动;因为金属屏蔽罩务必焊在接路面上,并且务必与零组件维持一个适度的间距,因而必须占有珍贵的PCB板室内空间。

尽量确保金属屏蔽罩的详细十分关键,因此进到金属屏蔽罩的大数字电源线应当尽量走里层,并且最好是将数据信号路线层的下一层设成接地质构造。RF电源线能够从金属屏蔽罩底端的小空缺和接地装置开口处的走线层布线出来,但是开口处周边要尽量被众多的接地装置总面积包围着,不一样数据信号层上的接地装置可意谓好几个过孔连在起。虽然有之上的缺陷,可是金属屏蔽罩依然十分合理,并且经常是防护重要电路的唯一解决方法。

05 电源去耦电路

适当而合理的集成ic电源去耦(decouple)电路也十分关键。很多融合了线形路线的RF集成ic对电源的噪声十分比较敏感,一般每一个集成ic都必须选用达到四个电容器和一个防护电感来滤掉所有的电源噪声。

最少电容器值一般在于电容器自身的串联谐振和接脚电感,C4的值便是由此挑选的。C3和C2的值因为其本身接脚电感的关联而相对性较为大,进而RF去耦实际效果要差一些,但是他们较合适于滤掉较低頻率的噪声数据信号。RF去耦则是由电感L1进行的,它使RF数据信号没法从电源插头藕合到集成ic中。由于全部的布线全是一条潜在性的既可接受也可发送RF数据信号的无线天线,因此,将射频信号与关键线路、零组件防护是务必的。

这种去耦部件的实体部位一般也很重要。这好多个关键部件的合理布局标准是:C4要尽量挨近IC接脚并接地装置,C3务必挨近C4,C2务必挨近C3,并且IC接脚与C4的联接布线要尽量短,这好多个部件的接地装置端(尤其是C4)一般理应意谓表面下第一个接地质构造与集成ic的接地装置脚相接。将部件与接地质构造相接的过孔应当尽量挨近PCB板上的部件焊层,最好应用打在焊层上的埋孔将电极连接线电感减到最少,电感L1应当挨近C1。

一个集成化电路或放大仪经常具备一个集电结引路輸出(opencollector),因而必须一个上拽电感(pullupinductor)来出示一个高特性阻抗RF负荷和一个低特性阻抗直流稳压电源,一样的标准也适用对这一电感的电源端开展去耦。一些集成ic必须好几个电源才可以工作中,因而将会必须两到三套电容器和电感来各自对他们开展去耦解决,假如该集成ic周边沒有充足的室内空间,那麼去耦实际效果将会不佳。特别是在必须需注意的是:电感非常少平行面靠在一起,由于这将产生一个空芯变电器,并互相磁感应造成电磁干扰,因而他们中间的间距最少要等于在其中之一的高宽比,或是成斜角排序令其其互感减到最少。

射频电路板设计、打样生产可以联系电话:16681598897,也可以加微信直接联系